Fault-tolerant CAN Transceiver

# **Application Hints**

# **Fault-tolerant CAN Transceiver**

# PCA82C252 / TJA1053 / TJA1054 / TJA1054A

Version 3.1

Date : 23<sup>rd</sup> of November 2001

Application Hints FTCAN 3\_1.PDF

### Fault-tolerant CAN Transceiver

# **Revision History**

#### Changes Version 1.0 -> 2.0 :

- 1. Chapter 3, calculation examples for PCA82C252 and TJA1053 added, new aspects

- 2. Chapter 4, calculation hints for termination resistors added, new aspects

#### Changes Version 2.0 -> 2.1 :

- 1. Chapter 6 added

- 2. Chapter 7 added

- 3. Chapter 8 added

#### Changes Version 2.1 -> 2.2 :

- 1. Chapter 5, clarification that external ESD diodes are optional for further improvements

- 2. Chapter 8 added, Software design hints (previous chapter 8 re-numbered to chapter 9)

- 3. Chapter 9, FAQ 9.6, No communication at CANH to VCC short circuit

#### Changes Version 2.2 -> 3.0 :

- 1. Foreword added

- 2. Chapter 2 added, Upgrading Note TJA1053 -> TJA1054

- Chapter 3 added, Mode Control of the TJA1054

Chapter 5, formula 11 corrected, calculation example updated

- 5. Chapter 10, Software design hints dealing with the pin ERR added

#### Changes Version 3.0 -> 3.1 :

- 1. Editorial changes

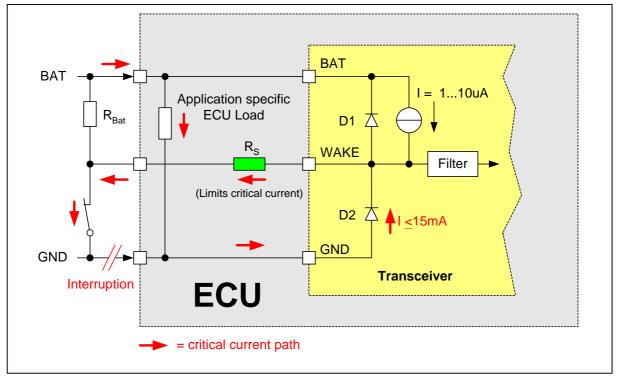

- 2. Chapter 8, series resistor at pin WAKE, more details

- 3. Chapter 9 added, series resistor at pins TXD

# Foreword

In this document, application related information for the various fault-tolerant transceiver implementations from Philips Semiconductors is collected. The different transceivers are a result of a continuous improvement of the fault-tolerant and system performance.

The first available product in the market was the PCA82C252, followed by the TJA1053 and later on by the TJA1054. In the mean time even the TJA1054 has become improved with respect to ESD capabilities. The so-called TJA1054A behaves identical to the TJA1054 but offers a higher ESD robustness on the bus-related pins. Thus wherever the TJA1054 is mentioned within this document it could also be read as TJA1054A, except in case a certain transceiver type is mentioned explicitly.

# Fault-tolerant CAN Transceiver

# Table of Contents :

|    | Comparison PCA82C252 / TJA1053 / TJA1054 / TJA1054A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                         |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|    | 1.1. System parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                         |

|    | 1.2. Device parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | .6                                                                                                                                      |

| 2  | Upgrading a TJA1053 Design with the TJA1054                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7                                                                                                                                       |

|    | 2.1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                                                                                                                                       |

|    | 2.2. Hardware Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                         |

|    | 2.2.1. External Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                         |

|    | 2.2.2. Wake-up sensitivity at pin WAKE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                         |

|    | 2.2.3. Current consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                         |

|    | 2.2.4. Operating Voltage Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                         |

|    | 2.3. Software Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                         |

|    | 2.3.1. Error signalling via pin ERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                         |

|    | 2.3.1.1. Software polls pin ERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <br>a                                                                                                                                   |

|    | 2.3.1.2. Software reads pin ERR during CAN interrupt service only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                         |

|    | 2.3.2. VCC Standby / PWON Standby                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                         |

|    | 2.3.3. First Battery Connection, behaviour of pin INH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                                                                                                                       |

|    | 2.3.4. Goto-Sleep / Wake-up Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                         |

|    | 2.3.5. Other issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                         |

|    | 2.3.5. Other issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10                                                                                                                                      |

|    | 2.4.1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                                                                                                                                      |

|    | 2.4.2. Hardware Interoperability Investigations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                                                                                                                                      |

|    | 2.4.3. Results of Hardware Interoperability Investigations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11                                                                                                                                      |

|    | 1.5. Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                         |

|    | 1.6. Migration Checklist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                         |

|    | с.<br>С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                         |

|    | Mode Control with the TJA1054                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                         |

|    | 3.1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                         |

|    | 3.2. Operating Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                         |

|    | 3.2.1. Normal Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14                                                                                                                                      |

|    | 2.2.2. Coto Elean                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                         |

|    | 3.2.2. Goto Sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15                                                                                                                                      |

|    | 3.2.3. Stby Sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15<br>15                                                                                                                                |

|    | 3.2.3. Stby Sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15<br>15<br>15                                                                                                                          |

|    | 3.2.3. Stby Sleep<br>3.2.4. PWON Stby<br>3.3. System Wake-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15<br>15<br>15<br>15                                                                                                                    |

|    | 3.2.3. Stby Sleep<br>3.2.4. PWON Stby<br>3.3. System Wake-up.<br>3.3.1. Local wake-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15<br>15<br>15<br>15<br>15                                                                                                              |

| ;  | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15<br>15<br>15<br>15<br>15                                                                                                              |

|    | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 15<br>15<br>15<br>15<br>15                                                                                                              |

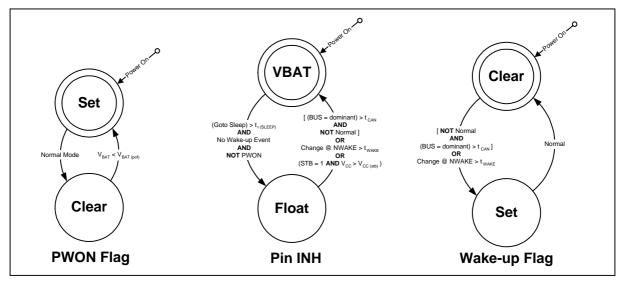

|    | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4. State diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15<br>15<br>15<br>15<br>15<br>15                                                                                                        |

|    | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4. State diagrams         3.4.1. PWON Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15<br>15<br>15<br>15<br>15<br>15<br>15<br>16                                                                                            |

|    | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4. State diagrams         3.4.1. PWON Flag         3.4.2. Pin INH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15<br>15<br>15<br>15<br>15<br>15<br>16<br>16                                                                                            |

|    | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4. State diagrams         3.4.1. PWON Flag         3.4.2. Pin INH         3.4.3. Wake-up Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16                                                                                      |

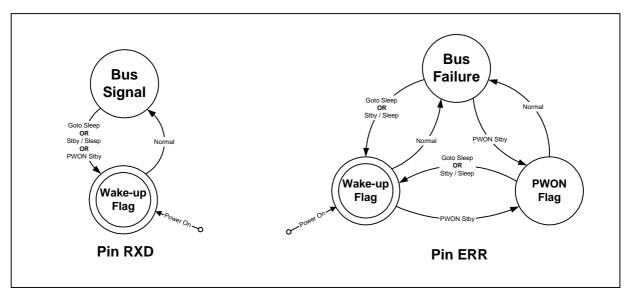

|    | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4. State diagrams         3.4.1. PWON Flag         3.4.2. Pin INH         3.4.3. Wake-up Flag         3.4.4. Pin RXD                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16                                                                                |

|    | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4. State diagrams         3.4.1. PWON Flag         3.4.2. Pin INH         3.4.3. Wake-up Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16                                                                                |

| :  | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4. State diagrams         3.4.1. PWON Flag         3.4.2. Pin INH         3.4.3. Wake-up Flag         3.4.4. Pin RXD         3.4.5. Pin ERR                                                                                                                                                                                                                                                                                                                                                                                                                  | 15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16<br>17                                                                          |

| 4. | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4. State diagrams         3.4.1. PWON Flag         3.4.2. Pin INH         3.4.3. Wake-up Flag         3.4.4. Pin RXD                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16<br>17<br><b>18</b>                                                             |

| 4. | 3.2.3. Stby Sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16<br>17<br><b>18</b><br>18                                                       |

| 4. | 3.2.3. Stby Sleep       3.2.4. PWON Stby         3.3. System Wake-up       3.3.1. Local wake-up         3.3.1. Local wake-up       3.3.2. Remote wake-up         3.3.2. Remote wake-up       3.3.3. Mode change         3.4. State diagrams       3.4.1. PWON Flag         3.4.2. Pin INH       3.4.3. Wake-up Flag         3.4.3. Wake-up Flag       3.4.4. Pin RXD         3.4.5. Pin ERR       7         Vcc Supply and Recommended Bypass Capacitance         4.1. List of used Abbreviations       7                                                                                                                                                                                                                           | 15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16<br>17<br><b>18</b><br>18                                                       |

| 4. | 3.2.3. Stby Sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15<br>15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16<br>17<br><b>18</b><br>19<br>20                                           |

| 4. | 3.2.3. Stby Sleep       3.2.4. PWON Stby         3.3. 2.4. PWON Stby       3.3.1. Local wake-up         3.3.1. Local wake-up       3.3.2. Remote wake-up         3.3.2. Remote wake-up       3.3.3. Mode change         3.4.1. PWON Flag       3.4.1. PWON Flag         3.4.2. Pin INH       3.4.3. Wake-up Flag         3.4.3. Wake-up Flag       3.4.4. Pin RXD         3.4.5. Pin ERR       4.1. List of used Abbreviations         1.2. Summary       1.3. Average Supply Current at Absence of Bus Short-Circuit Conditions                                                                                                                                                                                                    | 15<br>15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16<br>17<br>18<br>19<br>20                                                  |

| 4. | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4.1. PWON Flag         3.4.1. PWON Flag         3.4.2. Pin INH         3.4.3. Wake-up Flag         3.4.4. Pin RXD         3.4.5. Pin ERR         Vcc Supply and Recommended Bypass Capacitance         4.1. List of used Abbreviations         1.2. Summary         1.3. Average Supply Current at Absence of Bus Short-Circuit Conditions         1.3.1. Maximum dominant supply current (without bus wiring faults)                                                                                                                                        | 15<br>15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16<br>17<br>18<br>19<br>20<br>20                                            |

| 4. | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4. State diagrams         3.4.1. PWON Flag         3.4.2. Pin INH         3.4.3. Wake-up Flag         3.4.4. Pin RXD         3.4.5. Pin ERR         Vcc Supply and Recommended Bypass Capacitance         4.1. List of used Abbreviations         1.2. Summary         1.3. Average Supply Current at Absence of Bus Short-Circuit Conditions         1.3.1. Maximum dominant supply current (without bus wiring faults)         1.3.2. Thermal considerations (without bus wiring faults)         1.3.2. Thermal considerations (without bus wiring faults) | 15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16<br>16<br>17<br><b>18</b><br>19<br>20<br>20<br>20<br>20<br>20 |

| 4. | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4.1. PWON Flag         3.4.2. Pin INH         3.4.3. Wake-up Flag         3.4.4. Pin RXD         3.4.5. Pin ERR         Vcc Supply and Recommended Bypass Capacitance         4.1. List of used Abbreviations         1.2. Summary         1.3. Average Supply Current at Absence of Bus Short-Circuit Conditions         1.3.1. Maximum dominant supply current (without bus wiring faults)         1.3.2. Thermal considerations (without bus wiring faults)                                                                                               | 15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>15<br>16<br>16<br>16<br>16<br>16<br>17<br><b>18</b><br>19<br>20<br>20<br>20<br>20<br>20 |

| 4. | 3.2.3. Stby Sleep         3.2.4. PWON Stby         3.3. System Wake-up         3.3.1. Local wake-up         3.3.2. Remote wake-up         3.3.3. Mode change         3.4. State diagrams         3.4.1. PWON Flag         3.4.2. Pin INH         3.4.3. Wake-up Flag         3.4.4. Pin RXD         3.4.5. Pin ERR         Vcc Supply and Recommended Bypass Capacitance         4.1. List of used Abbreviations         1.2. Summary         1.3. Average Supply Current at Absence of Bus Short-Circuit Conditions         1.3.1. Maximum dominant supply current (without bus wiring faults)         1.3.2. Thermal considerations (without bus wiring faults)         1.3.2. Thermal considerations (without bus wiring faults) | 15515516666167<br><b>18</b> 19022022121                                                                                                 |

# Fault-tolerant CAN Transceiver

| <ul> <li>1.4.2.1. Example calculation</li> <li>1.4.3. Vcc extra supply current in single fault condition</li></ul> | 22<br>23<br>23<br>23<br>24<br>24<br>24<br>25<br>25                         |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

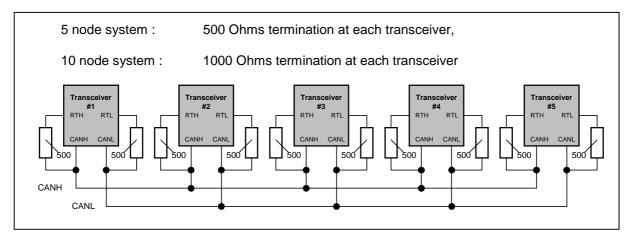

| <ul> <li>5.1. How to dimension the Bus Termination Resistor values, some basic rules</li></ul>                     | 26<br>27<br>28<br>28<br>28<br>28<br>28<br>28<br>28<br>28<br>28<br>28<br>28 |

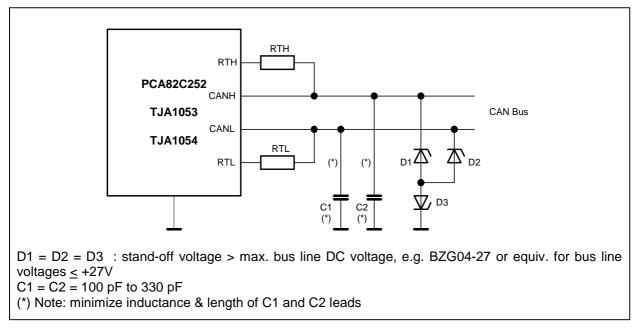

| 6. ESD Protection<br>6.1. Improved ESD capability of TJA1054A                                                      |                                                                            |

| 6.2. Optional external ESD Improvement                                                                             |                                                                            |

|                                                                                                                    | 30                                                                         |

| 6.2. Optional external ESD Improvement                                                                             | 30<br>31<br>32<br>33                                                       |

| <ul> <li>6.2. Optional external ESD Improvement</li></ul>                                                          | 30<br>31<br>32<br>33<br>33<br>34<br>34<br>34                               |

| <ul> <li>6.2. Optional external ESD Improvement</li></ul>                                                          | 30<br>31<br>32<br>33<br>33<br>34<br>34<br>34<br>34<br>34<br>34             |

# Fault-tolerant CAN Transceiver

| 12. Frequently Asked Questions                                 | 40 |

|----------------------------------------------------------------|----|

| 12.1. The transceiver does not enter the Sleep Mode            |    |

| 12.2. System operates in Single Wire Mode all time             |    |

| 12.3. System does not wake-up, even if there is bus activity   |    |

| 12.4. Transceiver is damaged when external tools are connected |    |

| 12.5. CAN tool cannot communicate with certain application     |    |

| 12.6. No communication at CANH to VCC short circuit            |    |

### **Fault-tolerant CAN Transceiver**

# 1. Comparison PCA82C252 / TJA1053 / TJA1054 / TJA1054A

#### 1.1. System parameters

| Кеу                                                        | PCA82C252                      | TJA1053                     | TJA1054       |

|------------------------------------------------------------|--------------------------------|-----------------------------|---------------|

| System size                                                | 10 – 15 nodes <sup>1) 2)</sup> | 10 – 15 nodes <sup>2)</sup> | > 32 nodes    |

| Speed                                                      | 20 - <125 kbps <sup>3)</sup>   | 20 – 125 kbps               | 40 – 125 kbps |

| Emission                                                   | +                              | +                           | ++            |

| Immunity                                                   | +                              | +                           | ++            |

| TxD dominant monitoring                                    | no                             | yes                         | yes           |

| Extended bus failure<br>management<br>(CANH to Vcc)        | no                             | no                          | yes           |

| Resolved problem of<br>arbitration across open<br>failures | no                             | yes                         | yes           |

1) The limit is given by the performance during CANH to ground failures, which very much depends on the size and type of cable used.

- 2) The limit is given by the wake-up capability during CANH to ground failures, which very much depends on the values of the distributed terminations across the network. Therefore, exact figures of system size cannot be given.

- 3) With CANH to VBAT failures the delay of the dominant edge is increased. The maximum speed strongly depends on the inductance of the cable used.

| Кеу                               | PCA82C252         | TJA1053                                       | TJA1054           | TJA1054A          |  |

|-----------------------------------|-------------------|-----------------------------------------------|-------------------|-------------------|--|

| Current consumption in            | 6 mA (rec)        | 6 mA (rec)                                    | 7 mA (rec)        | 7 mA (rec)        |  |

| Normal Mode (I <sub>CC</sub> )    | 29 mA (dom)       | 29 mA (dom)                                   | 17 mA (dom)       | 17 mA (dom)       |  |

| Current consumption in            | 70 uA             | 70 uA                                         | 30 uA             | 30 uA             |  |

| Standby Modes (I <sub>BAT</sub> + |                   |                                               |                   |                   |  |

| I <sub>CC</sub> )                 |                   |                                               |                   |                   |  |

| Minimum operating                 | 6V                | 6V                                            | 5V                | 5V                |  |

| voltage                           |                   |                                               |                   |                   |  |

| Prevention of VBAT                | no                | no                                            | yes               | yes               |  |

| reverse current <sup>1)</sup>     |                   |                                               |                   |                   |  |

| WAKE sensitivity                  | negative edge     | negative edge                                 | both edges        | both edges        |  |

| Vcc Standby mode                  | yes               | yes                                           | no                | no                |  |

| ERR reporting of open             | during frame only | during frame only                             | during frame and  | during frame and  |  |

| failures                          |                   |                                               | inter frame space | inter frame space |  |

| ESD Protection pins               | 2kV Human Body    | an Body   2kV Human Body   2kV Human Body   4 |                   | 4kV Human Body    |  |

| RTH / RTL / CANH /                | 200V Machine M.   | 200V Machine M.                               | 200V Machine M.   | 300V Machine M.   |  |

| CANL                              |                   |                                               |                   |                   |  |

### 1.2. Device parameters

In case a module looses its battery connection, a reverse power supply of this module via the CAN bus lines is prevented. For the PCA82C252 and the TJA1053 an external diode at the battery pin of the transceiver is required. This diode is required additionally to the control unit's polarity protection diode typically implemented at the battery connector of the entire module.

### Fault-tolerant CAN Transceiver

# 2. Upgrading a TJA1053 Design with the TJA1054

#### 2.1. Overview

The TJA1054 is a fault-tolerant CAN transceiver suitable for networks including up to 32 nodes and is the compatible successor of the well-known TJA1053. Compared with the TJA1053, the TJA1054 provides several enhanced features:

- Extremely reduced electro-magnetic emission (EME)

- Very good electro-magnetic immunity (EMI)

- Enhanced bus failure management (short circuits to 5V are tolerated)

- Improved error signalling

- Improved behaviour during "Loss of Power" situations

The TJA1054 is designed to be downward compatible to the TJA1053 and can be used in most of the existing TJA1053 applications without any changes in hardware and software. Nevertheless, due to the enhanced functionality there are some points to be considered if the TJA1053 is replaced by the TJA1054.

The following chapters discuss all hardware and software issues in detail in order to allow a smooth migration from the TJA1053 to the TJA1054.

Special attention is paid to interoperability issues giving the confidence that both devices can be used simultaneously within one network. Validation showed that a "step-by-step" introduction of the TJA1054 into an existing TJA1053 system can be made without risk.

#### 2.2. Hardware Issues

#### 2.2.1. External Components

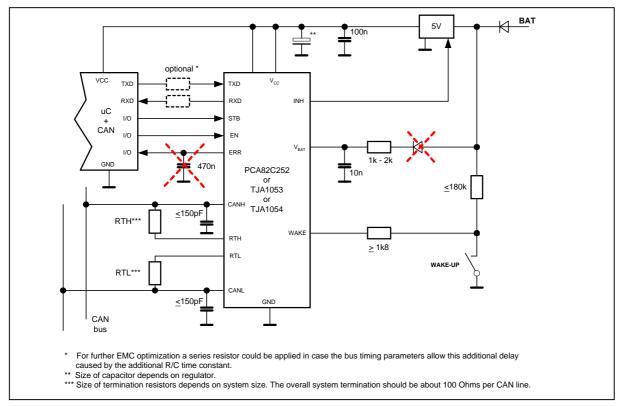

When the TJA1053 is replaced by a TJA1054, two external hardware components may be removed (see also figure 1) :

- Reverse current protection diode at pin BAT

- Pulse lengthening capacitor at pin ERR

The extra diode for the TJA1053 is needed to suppress a reverse power supply of the control unit if the battery connection of the entire unit was lost. For the TJA1053, a current flow from the CANL bus line backward to the pin BAT of the transceiver was possible if the transceiver was not powered. In some applications, this reverse current was high enough to supply the microcontroller unintentionally. The TJA1054 is internally protected against such reverse currents making the diode superfluous.

Reading the pin ERR during the normal CAN interrupt service routine was not possible for the TJA1053 in case of "open failures" on the bus lines. Here, the so-called "acknowledge bit" of any valid CAN message cleared an already detected "open failure" at the pin ERR. Therefore, an external lengthening capacitor was required for the TJA1053 in order to keep the detected failure signal valid until the interrupt service routine was executed by the host uC.

The TJA1054 does not require this extra lengthening capacitor since the pin ERR now internally keeps the failure signal active. (see also 11.2.1.)

# Fault-tolerant CAN Transceiver

Figure 1 : Typical application circuitry using the TJA1053 and the TJA1054

#### 2.2.2. Wake-up sensitivity at pin WAKE

The wake-up input of the TJA1054 is sensitive on both edges, whereas the TJA1053 was sensitive on the falling edge only. This has typically no impact on the application since such external wake-up events are usually pulses including both edges.

Another improvement of the TJA1054 is that wake-up events have higher priority than the goto-sleep command. Systems using the TJA1053 may lose such a wake-up event. Consequently, a TJA1053 node may keep sleeping without starting the voltage regulator although a wake-up request has been driven to the pin WAKE. The TJA1054 will now recognise any wake-up event independently from the current command setting of the host CPU.

#### 2.2.3. Current consumption

The total current consumption of the TJA1054 is reduced compared to the TJA1053, especially during low-power modes. The slightly increased short circuit current of the CANH bus driver within the TJA1054 is compensated by its reduced normal mode supply current during dominant bus states. Thus, there is no impact to the applications power supply concept. But introduction of the TJA1054 provides a much lower sleep current per control unit now compared with the TJA1053.

| Condition                                                                  | TJA1053        | TJA1054        |

|----------------------------------------------------------------------------|----------------|----------------|

| Current consumption in Normal Mode, Icc                                    | 6 mA recessive | 7 mA recessive |

|                                                                            | 29mA dominant  | 17mA dominant  |

| Current consumption in Low-power Modes, $I_{\text{BAT}}$ + $I_{\text{CC}}$ | 70uA           | 30uA           |

#### 2.2.4. Operating Voltage Range

In order to increase the system performance during low battery conditions, the TJA1054 now allows operation down to 5V at the pin BAT, whereas the TJA1053 required at least 6V.

### Fault-tolerant CAN Transceiver

#### 2.3. Software Issues

#### 2.3.1. Error signalling via pin ERR

As already mentioned before, the behaviour of the error signalling at the pin ERR is improved within the TJA1054. This allows removing the external lengthening capacitor needed for the TJA1053 (see also 2.1). This new behaviour of the TJA1054 may have an impact on application software if the TJA1053 was used **without** external lengthening capacitor. Two scenarios are possible:

#### 2.3.1.1. Software polls pin ERR

Application software polling the pin ERR will see fewer transitions if the TJA1053 is replaced by the TJA1054. Especially during "open failures" on the bus lines, the software load caused by ERR events is reduced if the TJA1054 is used.

#### 2.3.1.2. Software reads pin ERR during CAN interrupt service only

Here, the "open failures" are now detected **and** signalled by the TJA1054 as desired, whereas the TJA1053 has signalled no problem. Thus, a simple migration to the TJA1054 automatically improves a software driven diagnosis function.

#### 2.3.2. VCC Standby / PWON Standby

The VCC Standby Mode known from the TJA1053 is replaced by the so-called PWON Standby Mode in the TJA1054 (STB = 1; EN = 0). There is no change in functionality between both transceivers except for the CANL biasing level. The TJA1053 drives 5V to CANL through pin RTL and the termination resistor, while the TJA1054 now drives 12V to CANL using the same path. This has no impact on the overall system performance if both transceivers are mixed in one network. Software is not influenced since both transceivers provide the same status information to the microcontroller via ERR and RXD.

#### 2.3.3. First Battery Connection, behaviour of pin INH

The TJA1053 allows to be set into Sleep Mode (INH floating) directly after first battery connection by driving the goto-sleep command to the control pins STB and EN ("01"). The TJA1054 needs to be set into Normal Mode before accepting the first goto-sleep command after first connection of the battery supply. After setting Normal Mode both devices behave identical concerning this item.

An internal power-on reset signal within the TJA1054 makes sure that the transceiver is reset successfully after power-up and the INH output is safely set to battery level. This internal reset signal is cleared whenever the Normal Mode is entered once. There are no special timing requirements to clear the internal reset signal thus software just has to set the Normal Mode via STB and EN followed by any other control code. Within most of the existing applications this is already implemented inside of the systems cold-start routines.

#### 2.3.4. Goto-Sleep / Wake-up Priority

The pin INH of the TJA1053 does ignore wake-up events in case these wake-up events are present while the goto-sleep command is continuously driven to the transceiver via pins STB and EN (STB = 0 / EN = 1). After the goto-sleep filter time ( see data sheets TJA1054/TJA1054A : "reaction time of goto sleep command" ) the INH flip-flop is continuously cleared thus setting the pin INH to a floating condition. Wake-up events are forwarded to INH first with releasing the goto-sleep command. Thus a systems voltage regulator connected to INH will become disabled even if there is a pending wake-up request. Nevertheless RXD and ERR will signal the wake-up event with a LOW output level independently from the pending goto-sleep command.

For the TJA1054 this behaviour is improved and no wake-up event is lost with respect to the pin INH. Within the TJA1054 the wake-up events have a higher priority than the goto-sleep command. Thus any wake-up event will reset INH to a HIGH output level independently from the goto-sleep command. RXD and ERR will reflect the wake-up condition with a LOW output level as known from the TJA1053.

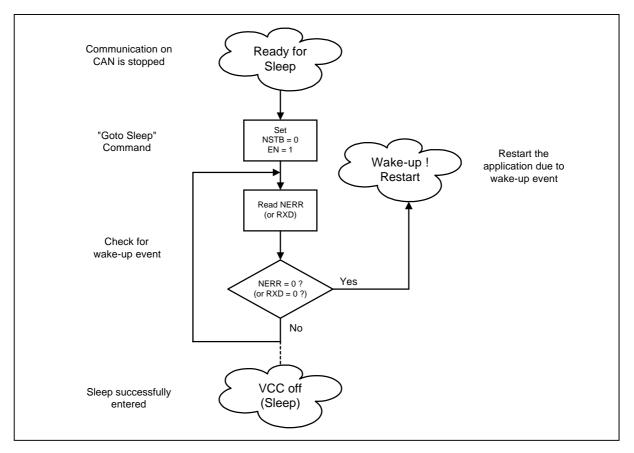

From software point of view it is highly recommended for both transceivers monitoring the pins RXD and/or ERR whenever the goto-sleep command was executed in order to detect a wake-up event

# Fault-tolerant CAN Transceiver

while the system should fall into sleep mode. INH might keep HIGH or become HIGH again caused by a wake-up event before the supply of the uC was successfully disabled. (see also 11.1.)

#### 2.3.5. Other issues

Experiences with different software drivers have shown the advantage to implement a kind of CAN communication monitoring in software, expecting CAN bus events in certain time frames. At least a reception of messages or successful transmissions should appear in order to get confidence, that the CAN bus is still operating properly. This is especially important for recovery from dual bus failure situations towards single bus failure situations.

Due to the automatic transmit message repetition mechanism of a CAN protocol engine it might happen that a node retransmits a message forever in case there is no acknowledge received from the bus. This continuously transmitting node might lock the bus system and thus prevents other nodes to recover from a dual bus failure situation towards a single bus failure situation.

Therefore, whenever there is no response from the CAN bus within a reasonable time, pending transmission requests should be aborted in software. This will increase the system availability during certain bus failure conditions, which require single wire operation.

### 2.4. Interoperability : Mixed Systems with TJA1053 and TJA1054

#### 2.4.1. Overview

During development of the TJA1054 special attention was paid to interoperability issues in order to allow a smooth migration of existing applications by simple replacement of the TJA1053. Particularly, the enhancements of the bus failure management (5V short circuits) have been included very carefully into the existing circuitry to avoid system hang-ups, if both transceivers are mixed in one system.

The TJA1054 is designed to replace the TJA1053 within running car series production without interoperability risk.

Interoperability of both devices has been proved in system simulation as well as in hardware investigation.

The key results of these investigations are :

- A pure TJA1054 network solves the known weaknesses of a TJA1053 system (wake-up of big networks with failure HxGND, short circuits to 5V .... )

- A mixed system of TJA1053 and TJA1054 has at least the same performance as the pure TJA1053 system; in some aspects the growing presence of TJA1054 nodes in the network even improves the overall system performance

- Taking into consideration the issues described in the previous chapters, mixed systems of both transceiver are possible at any ratio without restrictions

#### 2.4.2. Hardware Interoperability Investigations

In order to investigate interoperability issues of the transceiver, a network with 25 nodes was set up and investigated in detail. A typical topology including star points was chosen according to real automotive applications. This topology includes cable stubs with more than 5 meters and more than 55 meters overall cable length.

Worst case scenarios were analysed including weak bus failure conditions, double failures, ground shifts and power supply drops. Especially, operating mode changes (Normal Mode / Standby / Sleep) were performed simultaneously with bus failure situations.

# Fault-tolerant CAN Transceiver

#### 2.4.3. Results of Hardware Interoperability Investigation

The following table gives an overview about the mixed system investigations using the TJA1053 together with the TJA1054 in different mixing ratios. An assessment is made compared with a pure TJA1053 system with same topology.

| В  | us Failure | Standard Communication<br>(incl. resistive failures ) | Communication with<br>Ground Shift (+/- 1.5V) | Communication at<br>Low Battery Voltages | Mode Changes / Wake-up<br>combined with Bus<br>Failure Conditions | Communication with local<br>Loss of Termination |

|----|------------|-------------------------------------------------------|-----------------------------------------------|------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------|

| 0  | none       | ✓                                                     | ✓                                             | ✓                                        | ✓                                                                 | ✓                                               |

| 1  | Н//        | ✓                                                     | √                                             | ✓                                        | ٢                                                                 | 0                                               |

| 2  | L//        | ✓                                                     | ✓                                             | ✓                                        | ✓                                                                 | ✓                                               |

| 3  | HxBAT      | Ö                                                     | ✓                                             | ✓                                        | ✓                                                                 | ✓                                               |

| 3a | HxVCC      | ٢                                                     | Ü                                             | ٢                                        | 0                                                                 | C                                               |

| 4  | LxGND      | ✓                                                     | $\odot$                                       | ✓                                        | ✓                                                                 | ✓                                               |

| 5  | HxGND      | ✓                                                     | ~                                             | ✓                                        | ٢                                                                 | ✓                                               |

| 6  | LxBAT      | ✓                                                     | ٢                                             | ✓                                        | ✓                                                                 | ✓                                               |

| 6a | LxVCC      | ✓                                                     | ~                                             | ✓                                        | ٢                                                                 | ✓                                               |

| 7  | HxL        | 1                                                     | 1                                             | ✓                                        | ✓                                                                 | <ul> <li>✓</li> </ul>                           |

#### Key :

( ) mixed system behaves **better** than a pure TJA1053 system

( ✓ ) mixed system behaves equal to a pure TJA1053 system

( 🕅 ) mixed system behaves **worse** than a pure TJA1053 system

#### 2.5. Conclusion

Both transceivers, TJA1053 and TJA1054, are interoperable and can be used simultaneously within the same network. This allows migrating gradually from TJA1053 to TJA1054 in running car mass production.

Due to new features introduced with the TJA1054, existing TJA1053 applications need to be reviewed according to the comments within this report before replacing the transceiver.

# Fault-tolerant CAN Transceiver

# 2.6. Migration Checklist

| Item                                                    | TJA1053                                                                                          | TJA1054                                                                           | Comment                                                                                                                                                     |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Diode @ pin BAT                                         |                                                                                                  |                                                                                   | no reverse power supplying by TJA1054                                                                                                                       |

| Capacitor @ pin ERR                                     | depends on<br>software                                                                           | can be removed                                                                    | function is integrated into the TJA1054                                                                                                                     |

| Sensitivity of pin WAKE                                 | falling edge only                                                                                | ing edge only both edges check behaviour of sy via pin WAKE                       |                                                                                                                                                             |

| Goto-sleep command<br>after first battery<br>connection |                                                                                                  |                                                                                   | Internal power-on signal has to be<br>cleared by setting the TJA1054 into<br>Normal Mode after first battery<br>connection                                  |

| Goto-sleep command,<br>priority of wake-up event        | INH becomes<br>floating the time<br>goto-sleep is driven<br>even if there is a<br>wake-up coming | INH keeps HIGH if<br>there is a wake-up<br>coming during goto-<br>sleep is driven | It is recommended to monitor pin<br>RXD and/or pin ERR after goto-<br>sleep in order to detect a wake-up<br>event during the transition into<br>Sleep Mode. |

### Fault-tolerant CAN Transceiver

# 3. Mode Control with the TJA1054

#### 3.1. Overview

The fault tolerant CAN transceiver TJA1054 provides an integrated functionality controlling an external voltage regulator in order to design low power CAN bus systems with remote and local wake-up capabilities. A dedicated INH pin allows disabling the entire power supply of a control unit, thus reducing the overall system power consumption to a minimum. The transceiver is the only supplied component during such a low-power state.

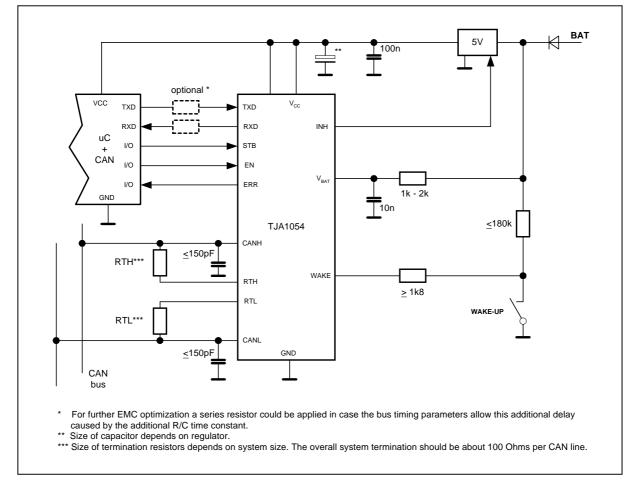

Following figure shows an application example using the TJA1054.

Figure 2 : Typical application of the TJA1054

As shown within Figure 2 the transceiver is powered directly from the battery supply via the pin BAT. This allows disabling the VCC supply entirely during time phases, the CAN bus is not required by the system. Therefore two control pins STB and EN coming from the host microcontroller are used to control the actual mode of operation like normal communication or low-power operation. For wake-up purposes a battery-related WAKE pin is provided.

In addition to bus failure information and the CAN received bit stream, the pins ERR and RXD are used to signal wake-up requests towards the application controller.

# Fault-tolerant CAN Transceiver

### 3.2. Operating Modes

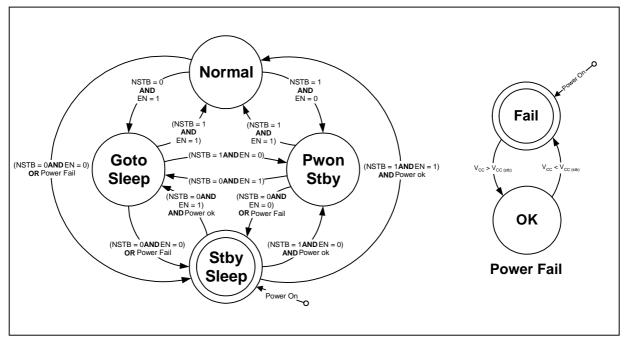

The two fail-safe coded pins STB and EN mainly control the power management of the TJA1054. They are defining directly the actual mode of operation as illustrated within Figure 3. The following operating modes are implemented:

- Normal Mode normal transceiver operation

- Goto Sleep disables the external voltage regulator via INH after a certain time out

- Stby Sleep similar to Goto Sleep, but INH is not affected

- PWON Stby similar to Stby Sleep, but allows to read back the PWON flag indicating a power-on condition

All modes different from Normal Mode are low-power modes reducing the current consumption significantly.

Figure 3 : Operating Modes of the TJA1054

Note, that a change from the power-on condition (STB and EN = "0") is possible only, if the VCC supply is present. Whenever VCC falls below a certain level (see data sheet TJA1054: "supply voltage for forced Standby Mode") the fail-safe Standby Mode is entered automatically (power-fail). Depending on the selected mode of operation, the I/O pins provide different information for the application as described within the next chapters.

#### 3.2.1. Normal Mode

During normal mode the transceiver is used to transmit data to the bus and to receive data from the CAN bus. Here the pin RXD reflects the bus signal and the pin ERR is used to signal bus failure conditions with an active LOW behaviour.

# Fault-tolerant CAN Transceiver

#### 3.2.2. Goto Sleep

Entering Goto Sleep the transceiver immediately changes into low-power operation, while the pin INH is still kept active HIGH. Now an internal wake-up flip-flop is output via the pins RXD and ERR, if VCC is present. Thus both pin's signals can be used to wake-up the application with an active low signal. If the Goto Sleep state keeps present for a certain time (see data sheet TJA1054: "reaction time of goto-sleep command") the INH output of the TJA1054 becomes "floating" disabling the externally connected voltage regulator. The application can keep within the Goto Sleep state or switch over to Stby Sleep mode without any difference in behaviour of the transceiver.